Samsung expects chip performance gains from backside power delivery experiments.

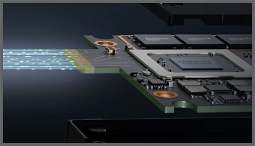

The Samsung Foundry team has detailed further its backside power delivery experiments, with the company reporting a 14.8% reduction in Chip area thanks to the technology. Backside power delivery enables thicker wires with lower resistance, driving higher currents for better Performance.

In a paper presented at the VLSI Symposium, Samsung reported on its backside power delivery (BPS) experiments. The company says that the reduction in area allows for either increased transistor density or cost reduction. It also observed a 9.2% reduction in wiring length, which the team says leads to additional performance advantages.

"In this paper, we report on the results of our BPS system implementation, which enables lower wiring resistances and higher power densities," says the team. "Our results show a 14.8% reduction in chip area with an additional 9.2% reduction in wiring length, leading to a total chip performance improvement of 2.6% at the same power."

It says that this is largely due to the fact that backside power delivery enables thicker wires with lower resistance, which in turn enables higher currents for better performance. It goes on to say that this also results in a reduction in block area by 2.4%, an improvement in block performance by 1.6%, and an increase in Fmax by 3.6%.

Intel has also detailed its own backside power delivery network called PowerVia, which it says will lead to "performance gains for advanced logic applications and increased power density for advanced memory and analog circuits."

With backside power delivery, shifting power rails to the rear and isolating them from I/O wiring reduces resistances, enhancing performance and saving energy. Samsung says that it is "currently developing BPS for 7nm and EUV-based 7nm" but has not disclosed when it plans to implement backside power delivery or with which node.

In the meantime, the company is working on its 2nd Generation 3nm-class gate-all-around transistors-based SF3 technology. It aims for mass production in 2024 and has SF3P and 2nm-class SF2 planned for 2025.

While it is possible that backside power delivery will come to 3nm, it seems unlikely. We will likely hear more about the technology when Samsung announces its plans for SF3P and SF2 in 2025.