Intel unveils new APX and AVX10

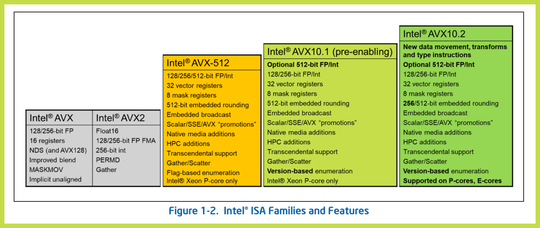

Intel unveils a new version of its Advanced Vector Extensions (AVX) vector instruction set, called AVX10. The new instruction set will be used by both P-cores and E-cores within its processors, bringing AVX-512 capabilities to both kinds of its chips. Previously, only P-cores were able to support AVX-512.

AVX10 will be Intel’s vector ISA of choice for future consumer and server processors. It will allow chips with both E-cores and P-cores to support AVX-512, with 512-bit instructions being limited to P-cores.

AVX10 is a superset of AVX-512, supporting 256-bit and 512-bit vector register sizes. The new instruction set includes AVX-512 vector instructions with a maximum vector register length of 256 bits.

E-cores are limited to the 256-bit vector length, while P-cores can use 512-bit vectors. Intel claims existing applications will perform the same with AVX10 as they did with AVX-512.

AVX10.1 will be supported by sixth-gen Xeon chips, transitioning from AVX-512 to AVX10. Future chips will support AVX10.2, which adds support for 256-bit vector lengths and other features.

Intel plans to simplify AVX10 enumeration methods and reduce version and enumeration bloat.

AVX-512 ISA will be frozen when AVX10 debuts, all future AVX-512 instructions will occur through AVX10.

Intel also introduces APX, which reduces loads and stores, improves register access, and repurposes unused area for XSAVE. APX implementation will not impact silicon area or power consumption of the CPU core.

The company says it is investigating slimming down the Intel 64 architecture to a simplified version named x86S.

You can find out more about AVX10 and APX in the main story below.